SONG Shenghui and MURCH Ross, Dept. of ECE, HKUST

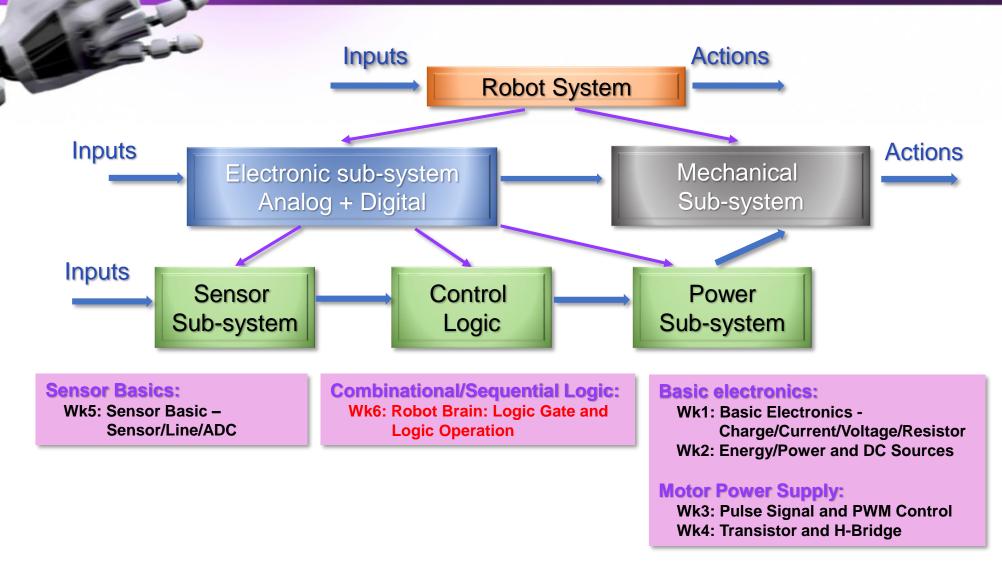

#### ELEC1100 ROADMAP

#### **BINARY NUMBER**

- Decimal number system base 10, each digital is selected from the set {0,1,2,3,4,5,6,7,8,9}

- Binary number system base 2, each digital is selected from the set {0,1}

| Multiplication and addition of binary number |   |   |  |   |   |   |

|----------------------------------------------|---|---|--|---|---|---|

| +                                            | 0 | 1 |  | * | 0 | 1 |

| 0                                            | 0 | 1 |  | 0 | 0 | 0 |

| 1                                            | 1 | 0 |  | 1 | 0 | 1 |

| Base 10 | Base 2 |

|---------|--------|

| 0       | 0000   |

| 1       | 0001   |

| 2       | 0010   |

| 3       | 0011   |

| 4       | 0100   |

| 5       | 0101   |

| 6       | 0110   |

| 7       | 0111   |

| 8       | 1000   |

| 9       | 1001   |

| 10      | 1010   |

### **BINARY NUMBER OPERATION**

| <ul> <li>Addition</li> </ul> |                | <ul> <li>Multiplica</li> </ul> | ation          |

|------------------------------|----------------|--------------------------------|----------------|

| Decimal                      | Binary         | Decimal                        | Binary         |

| 7<br>+ 5                     | 0111<br>+ 0101 | 7<br>× 5                       | 0111<br>× 0101 |

| 12                           | 1100           | 35                             | 0111<br>0111   |

|                              |                |                                | 100011         |

- Binary digit: 0 and 1 can be represented by logic (True or False)

- ➢ 0 is equivalent to False

- ➤ 1 is equivalent to True

- Use Boolean Algebra (which operates on {T,F}) to manipulate the binary digit operation

#### LOGIC GATES

- ✤ Two values for logic: True ("T") and False ("F")

- A logic input can be combined with another logic input in different ways to form a new logic output. We call this combination of the inputs as logic gates.

- There are seven fundamental logic gates:

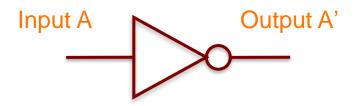

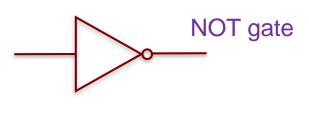

- ➢ Inverter (Not) − 1 input, 1 output

- ➢ AND 2 or more inputs, 1 output

- ➢ NAND 2 or more inputs, 1 output

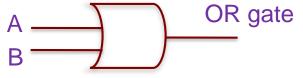

- ➢ OR − 2 or more inputs, 1 output

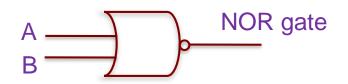

- ➢ NOR 2 or more inputs, 1 output

- ➤ XOR 2 or more inputs, 1 output

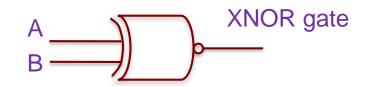

- ➤ XNOR 2 or more inputs, 1 output

#### TRUTH TABLE

- A tabular summary for all the possible outputs of a logic gate, given all the possible input values

- For a logic gate that has *n* inputs, how many possible input combinations do we have?

- Sometimes we use 0 to represent F and 1 to represent T

- Truth table of an inverter

| Input A | <b>Output A'</b> |

|---------|------------------|

| 0       | 1                |

| 1       | 0                |

#### AND/OR GATES

✤ AND gate: Output = A•B

A Output

| Α | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

e.g. if tmr is sunny and I finish ELEC 1100 hw, I'll go hiking.

OR gate: Output = A+B

| Α | B | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

e.g. if it rains tmr or I cannot finish ELEC 1100 hw, I'll stay home.

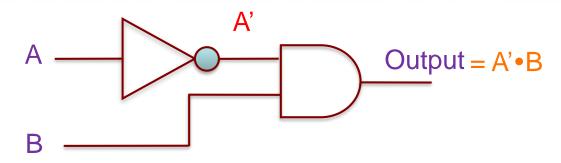

## EXAMPLE OF CIRCUIT WITH AND GATE

What is the output logic expression for the circuit below?

Complete the truth table

| Α | В | <b>A'</b> | Output |

|---|---|-----------|--------|

| 0 | 0 | 1         | 0      |

| 0 | 1 | 1         | 1      |

| 1 | 0 | 0         | 0      |

| 1 | 1 | 0         | 0      |

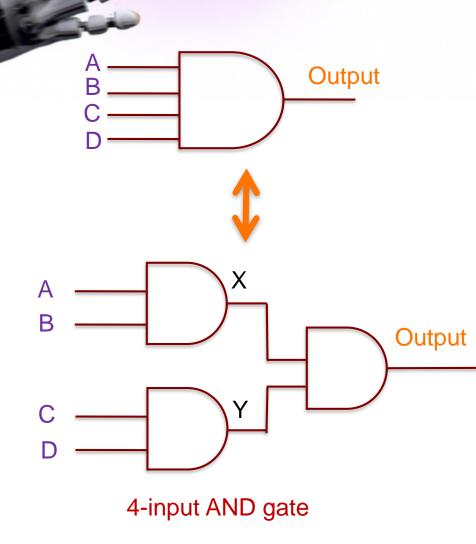

MORE EXAMPLE (AND GATE)

| Α | В | С | D | Output |

|---|---|---|---|--------|

| 0 | 0 | 0 | 0 | 0      |

| 0 | 0 | 0 | 1 | 0      |

| 0 | 0 | 1 | 0 | 0      |

| 0 | 0 | 1 | 1 | 0      |

| 0 | 1 | 0 | 0 | 0      |

| 0 | 1 | 0 | 1 | 0      |

| 0 | 1 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1 | 0      |

| 1 | 0 | 0 | 0 | 0      |

| 1 | 0 | 0 | 1 | 0      |

| 1 | 0 | 1 | 0 | 0      |

| 1 | 0 | 1 | 1 | 0      |

| 1 | 1 | 0 | 0 | 0      |

| 1 | 1 | 0 | 1 | 0      |

| 1 | 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1 | 1      |

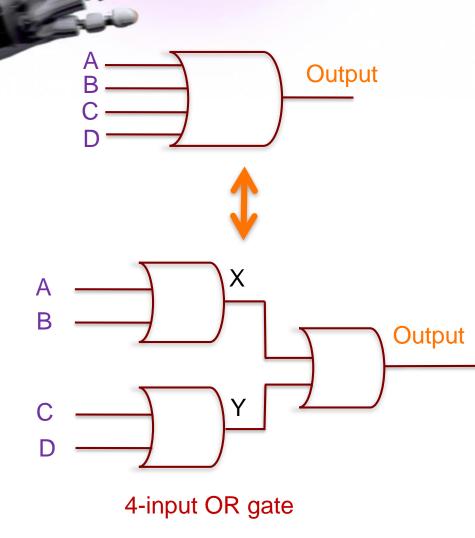

MORE EXAMPLE (OR GATE)

| Α | В | С | D | Output |

|---|---|---|---|--------|

| 0 | 0 | 0 | 0 | 0      |

| 0 | 0 | 0 | 1 | 1      |

| 0 | 0 | 1 | 0 | 1      |

| 0 | 0 | 1 | 1 | 1      |

| 0 | 1 | 0 | 0 | 1      |

| 0 | 1 | 0 | 1 | 1      |

| 0 | 1 | 1 | 0 | 1      |

| 0 | 1 | 1 | 1 | 1      |

| 1 | 0 | 0 | 0 | 1      |

| 1 | 0 | 0 | 1 | 1      |

| 1 | 0 | 1 | 0 | 1      |

| 1 | 0 | 1 | 1 | 1      |

| 1 | 1 | 0 | 0 | 1      |

| 1 | 1 | 0 | 1 | 1      |

| 1 | 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 1 | 1      |

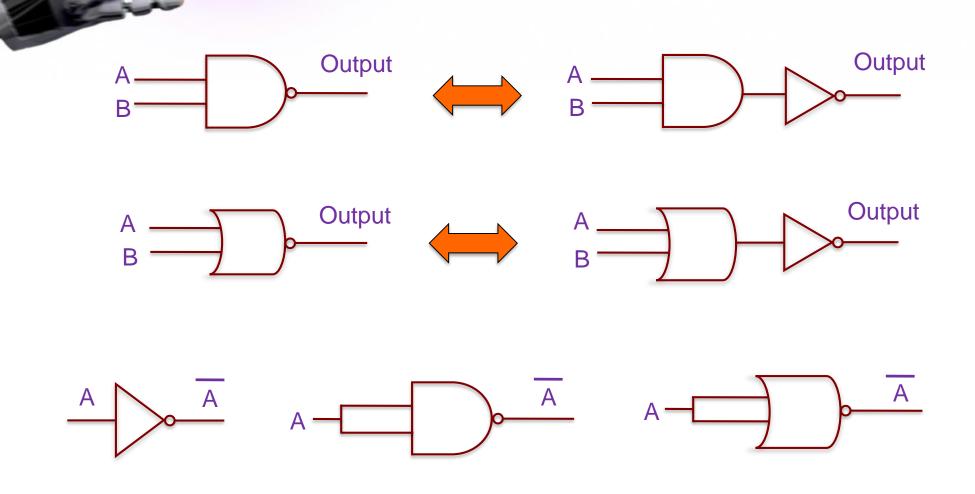

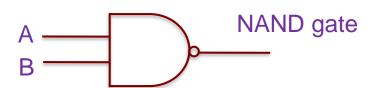

### NAND/NOR GATES

• NAND gate: Output =  $\overline{A \cdot B}$

| Α | B | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

• NOR gate: Output =  $\overline{A+B}$

| Α | B | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 0      |

SOME EQUIVALENT GATES

Ŵ

#### XOR/XNOR GATES

♦ XOR gate: Output =  $A \oplus B$

A \_\_\_\_\_Output

| Α | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

**\therefore** XNOR gate: Output =  $\overline{A \oplus B}$

| Α | B | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

#### LAW OF BOOLEAN ALBEGRA

- $\succ$  0+X = X

- ▶ 1+X = 1

- ≻ X'+X = 1

- $\succ 0 \bullet X = 0$

- $\succ$  1•X = X

- $\succ X \bullet X = X$

- $\succ X \bullet X' = 0$

- ≻ (X')' = X

- Exchange:

- $\succ$  X+Y = Y+X

- $\succ X \bullet Y = Y \bullet X$

- ✤ Associativity:

- $\succ X+(Y+Z) = (X+Y)+Z$

- $\succ X \bullet (Y \bullet Z) = (X \bullet Y) \bullet Z$

- Distributivity

- $\succ X \bullet (Y+Z) = X \bullet Y + X \bullet Z$

- DeMorgan's Law

- $\succ$  (X+Y)' = X'•Y'

- ≻ (XY)' = X'+Y'

(XY)'+(YZ)'+(XZ)' = (X'+Y') + (Y'+Z') + (X'+Z') = (XY)'+(XZ)'

$\succ$  (XY)'+(YZ)'+(XZ)' = (XY)'+(XZ)'

$X'+XY = (X \bullet (XY)')' = (X \bullet (X'+Y'))' = (X \bullet Y')' = X'+Y$

$\succ$  X'+XY = X'+Y

$(X+Y)\bullet(X+Z) = X\bullet X + X\bullet Z + Y\bullet X + Y\bullet Z = X\bullet(1+Z+Y) + Y\bullet Z = X+Y\bullet Z$

$\succ (X+Y)\bullet(X+Z) = X+Y\bullet Z$

$X \bullet (X+Y) = X \bullet X + X \bullet Y = X \bullet (1+Y) = X$

$\succ$  X•(X+Y) = X

$X + X \bullet Z = X \bullet (1 + Z) = X$

$\succ$  X+X•Z = X

LOGIC SIMPLIFICATION

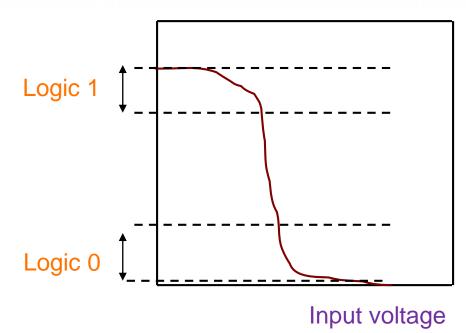

### VOLTAGE AND LOGIC VALUE

- How do we represent binary digital signals?

- We can use a range of voltage values to represent logic 0 or 1

- Sometimes we just use high voltage to represent 1 and low voltage to represent 0

#### Output voltage

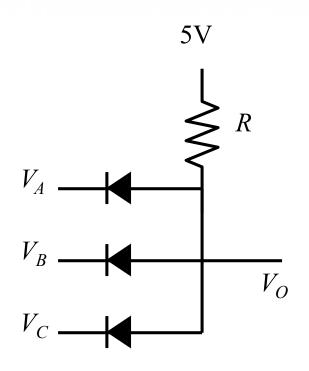

# LOGIC GATE CONSTRUCTION WITH DIODES

✤ AND gate

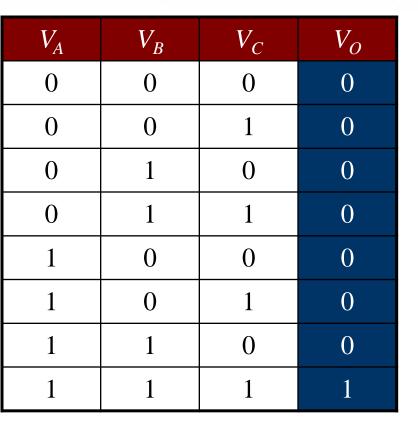

#### Input/Output Table

$$1 = 5V$$

$$0 = 0V$$

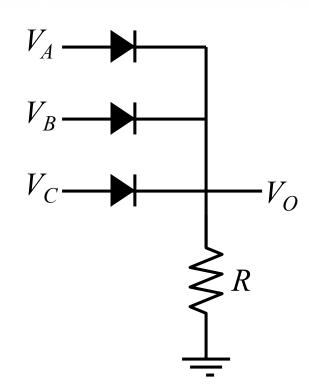

# LOGIC GATE CONSTRUCTION WITH DIODES [2]

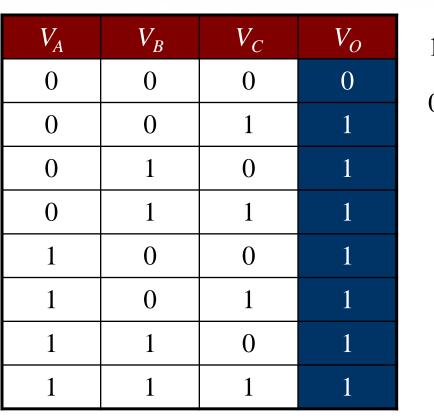

OR gate

#### Input/Output Table

$$1 = 5V$$

$$0 = 0V$$

### LECTURE SUMMARY

Binary digit: 0 and 1 can be represented by logic (True or False)

- > 0 is equivalent to False

- 1 is equivalent to True

A AND gate

## NEXT LECTURE

- ✤ K-map

- K-map simplification

## **QUESTIONS?**

72PA